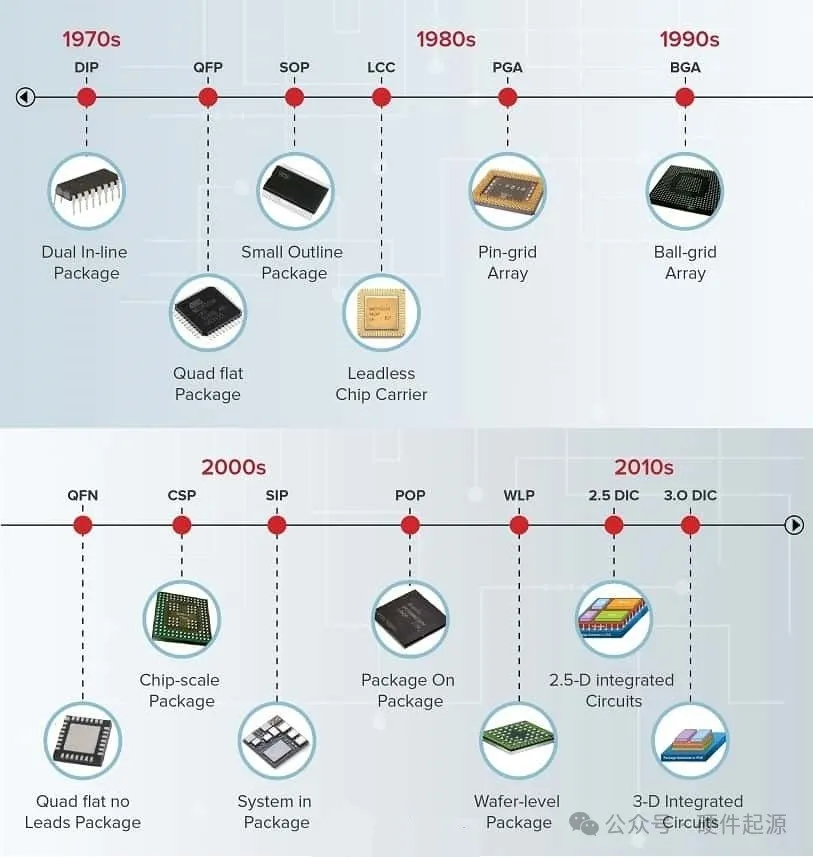

图1,半导体封装历史

图2,倒装芯片底部填充封装工艺

-

含铅焊料曾经普遍用于半导体封装,但由于环境问题,无铅焊料已成为标准。

-

铜通常用于各种互连,并且可以回收利用。

-

许多半导体封装使用塑料或聚合物材料进行封装、模塑料和封装结构。这些材料有时可以回收利用。

-

玻璃基板通常用于微机电系统(MEMS),回收玻璃可以减少半导体封装对环境的影响。 -

-

紧凑型设备:将组件集成到单个封装中可形成紧凑型设备,这对于智能手机和可穿戴设备等便携式设备尤其重要。 -

增强的性能:SiP 最大限度地缩短了互连长度,从而减少了信号延迟,这对于高速和高频应用至关重要。 更高的电源效率:除了减少信号互连的长度之外,SiP 内的配电网络也得到了更好的优化。这对于电池供电的设备至关重要。 降低制造成本:SiP 减少了电路板上需要组装的单个组件的数量,从而降低了总体制造成本。