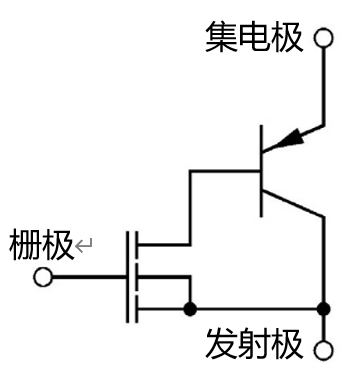

IGBT晶体管的结构要比 MOSFET 或双极结型晶体管 (BJT) 复杂得多。它结合了这两种器件的特点,并且有三个端子:一个栅极、一个集电极和一个发射极。就栅极驱动而言,该器件的行为类似于 MOSFET。它的载流路径与 BJT 的集电极-发射极路径非常相似。图 1 显示了 n 型 IGBT 的等效器件电路。

图 1. IGBT的等效电路

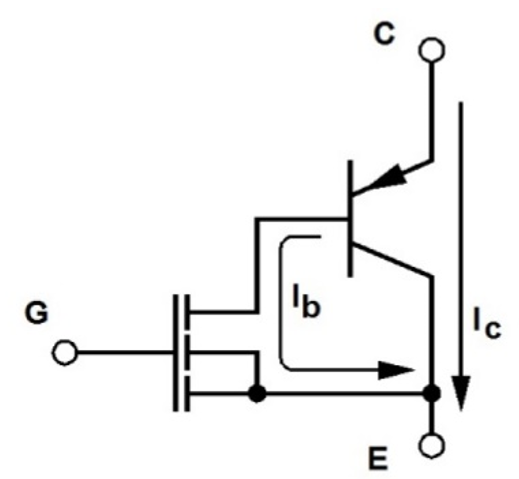

为了快速导通和关断 BJT,必须在每个方向上硬驱动栅极电流,以将载流子移入和移出基极区。当 MOSFET 的栅极被驱动为高电平时,会存在一个从双极型晶体管的基极到其发射极的低阻抗路径。这会使晶体管快速导通。因此,栅极电平被驱动得越高,集电极电流开始流动的速度就会越快。基极和集电极电流如图 2 所示。

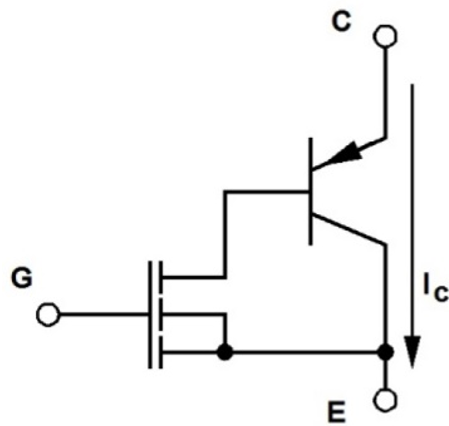

关断场景有点不同,如图 3 所示。当 MOSFET 的栅极电平被拉低时,BJT 中将没有基极电流的电流路径。基极电流的缺失会诱发关断过程;不过,为了快速关断,应强制电流进入基极端子。由于没有可用的机制将载流子从基极扫走,因此 BJT 的关断相对较慢。这导致了一种被称为尾电流的现象,因为基极区中存储的电荷必须被发射极电流扫走。

很明显,更快的栅极驱动 dv/dt 速率(源于更高的栅极电流能力)将会更快地接通和关断 IGBT,但对于器件的开关速度(特别是关断速度)而言,是存在固有限制的。正是由于这些限制,开关频率通常在 20kHz 至 50kHz 范围内,尽管在特殊情况下它们也可以用于更快和更慢的电路。IGBT 通常用于谐振和硬开关拓扑中的高功率 (Po > 1 kW) 电路。谐振拓扑最大程度降低了开关损耗,因为它们要么是零电压开关,要么是零电流开关。

较慢的 dv/dt 速率可以提高 EMI 性能(当涉及这方面问题时),并在导通和关断转换期间减少尖峰的形成。这是以降低效率为代价的,因为此时导通和关断的时间会比较长。

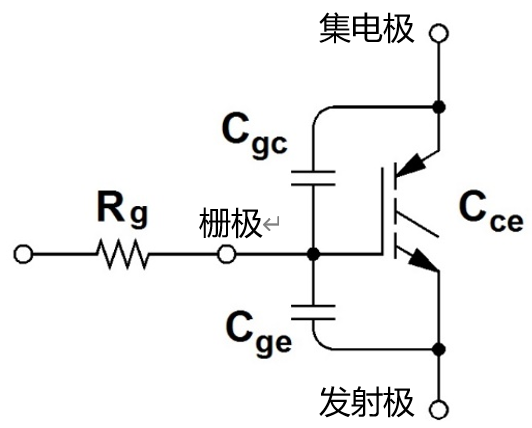

MOSFET 存在一种称为二次导通的现象。这是由于漏电压的 dv/dt 速率非常快,其范围可以在 1000–10000 V/us 之间。尽管 IGBT 的开关速度通常不如 MOSFET 快,但由于所使用的是高电压,因此它们仍然可以遭遇非常高的 dv/dt 电平。如果栅极电阻过高,就会导致二次导通。

在这种情况下,当驱动器将栅极电平拉低时,器件开始关断,但由于 Cgc 和 Cge 分压器的原因,集电极上的电压升高会在栅极上产生电压。如果栅极电阻过高,栅极电压可升高到足以使器件重新导通。这将导致大功率脉冲,从而可能引发过热,在某些情况下甚至会损坏器件。

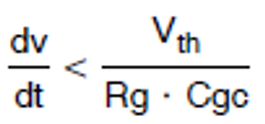

[参考文献1](公式1)

[参考文献1](公式1)

其中,

-

dv/dt 为关断时集电极上电压波形上升的速率

-

为栅极的平台电平

为栅极的平台电平

-

Rg为总栅极电阻

-

Cgc 为栅极-发射极电容

应注意,数据表上的 Ciss 是 Cge 和 Cgc 电容的并联等效值。

类似地,Rg 是栅极驱动器阻抗、物理栅极电阻和内部栅极电阻的串联和。内部栅极电阻有时可根据数据表计算出来。如果计算不出来,可通过以下方式进行测量:使用 LCR 电桥并使集电极-发射极引脚短路,然后在接近开关频率的频率下测量等效串联 RC。

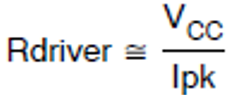

如果使用的是 FET 输出级,则可以在其数据表中找到驱动器阻抗。如果无法在数据表上找到,可通过将峰值驱动电流取为其额定 VCC 电平来进行近似计算。

(公式2)

(公式2)

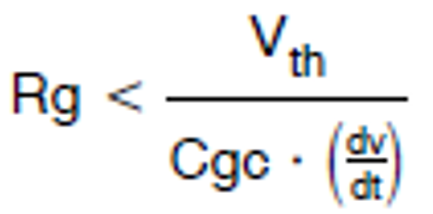

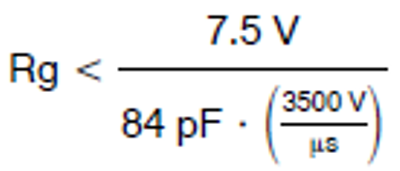

因此,最大总栅极电阻为:

(公式3)

(公式3)

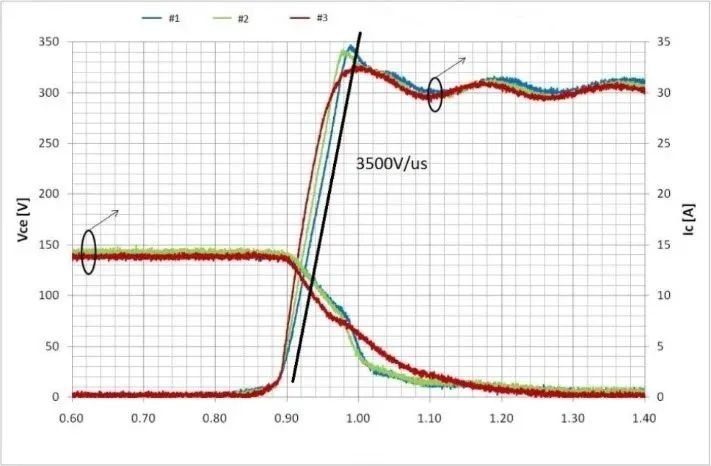

最大 dv/dt 是基于栅极驱动电流以及 IGBT 周围的电路阻抗。如果将高值电阻器用于栅极驱动,则需要在实际电路中进行验证。图 5 显示了同一电机控制电路中三个不同 IGBT 的关断波形。在此应用中,dv/dt 为 3500 V/s。

对于该情况而言,IGBT #2 的典型 Cgc 为 84 pF,而阈值栅极电压为 7.5 V(在 15 A 的条件下)。

(公式4)

因此,如果内部栅极电阻为 2Ω,驱动器阻抗为 5Ω,则所使用的绝对最大栅极电阻应为 18Ω。实际上,由于 IGBT、驱动器、板阻抗和温度的变化,建议采用一个较小的最大值(例如 12Ω)。

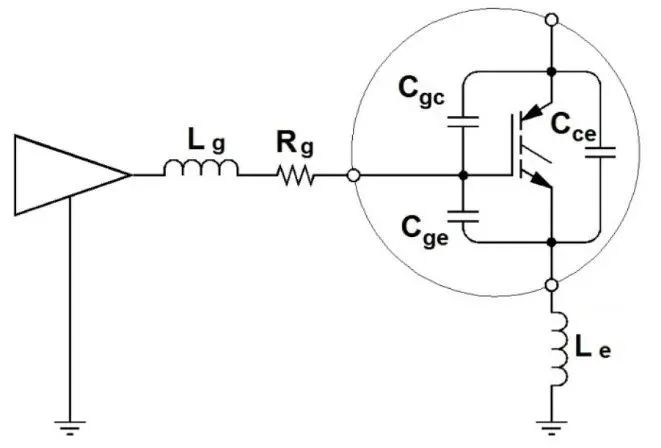

图 6. 等效栅极驱动电路

去除外部栅极电阻器可能会获得最佳的高频性能,同时确保不会发生二次导通。在某些情况下,这可能会起作用,但也可能由于栅极驱动电路中的阻抗而导致振荡。

栅极驱动电路为串联 RLC 谐振电路。电容主要源于 IGBT 寄生电容。所示的两个电感则源自 IGBT 和驱动器的板走线电感与焊线电感的组合。

在栅极电阻很小或没有栅极电阻的情况下,谐振电路将会振荡并造成 IGBT 中的高损耗。此时需要有足够大的栅极电阻来抑制谐振电路,从而消除振荡。

由于电感难以测量,因此也就很难计算适合的电阻。要最大程度降低所需的最小栅极电阻,最佳方案是采用良好的布局程序。

驱动器与 IGBT 栅极之间的路径应尽可能短。这适用于栅极驱动的整个电路路径以及接地回路路径。如果控制器不包括集成驱动器,则将 IGBT 驱动器置于 IGBT 的栅极附近要比将栅极驱动器的输入置于控制器的 PWM 输出端更为重要。从控制器到驱动器的电流非常小,因此相比从驱动器到 IGBT 的高电流和高 di/dt 电平所造成的影响,任何杂散电容的影响都要小得多。短而宽的走线是最大程度降低电感的最佳方式。

典型的最小驱动器电阻范围为 2Ω至 5Ω。这其中包括驱动器阻抗、外部电阻值和内部 IGBT 栅极电阻值。一旦设计好板的布局,即可确定并优化栅极电阻值。

本文给出了最大和最小栅极电阻值的指南。在这些限值之间有一个取值范围,藉此可以对电路进行调谐,从而获得最大效率、最小 EMI 或其他重要参数。在电路设计中取一个介于这些极值之间的安全值可确保设计的稳健。

[参考文献1](公式1)

为栅极的平台电平

(公式2)

(公式3)