MIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写,是MIPI联盟发起的为移动应⽤处理器制定的开放标准。MIPI采⽤高速串行接口传输数据,满⾜高分辨率摄像头的传输需求,采用串行接口方便PCB布局布线,提高信号完整性,也有利于减小PCB面积。MIPI接口的摄像头一般体积较小,适合于小型的嵌入式设备,比如手机和行车记录仪等,同时也广泛应用到AI端上推理设备。本文以百度的端上推理设备EdgeBoard作为原型来介绍MIPI相关技术的开发。如果用户购买EdgeBoard,出厂的镜像中带有MIPI的功能,只需再购买推荐的MIPI摄像头,即可实现即插即用。

MIPI接口分为两类,一是DSI (Display SerialInterface),提供处理器和显示模组之间的高速串行接口;二是CSI (Camera Serial Interface),提供处理器和摄像模组之间的高速串行接口。本文将要介绍的是CSI-2。

MIPI信号采用低压差分信号进行传输,具有传输速率快,抗干扰能力强的特点。MIPI的传输模式分为低速信号模式和高速信号模式,低速信号用于控制命令(10 MHz),高速信号用于数据传输(80Mbps -1Gbps/lane)。时钟处于非连续工作状态,根据传输状态进行时钟的切换,这样可以极大地降低功耗。关于D-PHY可参考MIPI® Alliance Specification for D-PHY。

MIPI最多可支持4通道数据,同时配有IIC总线进行配置,收发接口如下图:

MIPI协议也是采用类似于以太网协议结构,采用分层设计的思想,分为PHY Layer,Protocal Layer和Application Layer。

MIPI传输的报文中定义了图像数据的类型/格式(Data type),这些类型/格式方便在调试的时候确定链路是否工作正常,常用的Data Type如下图,比如YUV的数据格式的标示符是0x18到0x1F,期间的数值定义了具体的格式,比如YUV422,YUV444等,具体可参考MIPI Alliance Specification for CameraSerial Interface 2。

MIPI的电平标准分为LP (Low Power)模式和HP(High Power)模式,LP模式下高电平最大值1.3V,最小1.1V,典型值为1.2V,HP模式下共模电平200mv,摆幅200mV。

1、Ultrascale系列的FPGA使用MIPI_PHY_DCI 的电平,digitalcontrol impedence,如果是mipi的数据率很高时,比如lane rate高于1000Mbps,需要开启100R的termination。

2、如果使用K7系列的芯片,由于其不支持MIPI_PHY_DCI电平,可以通过LVDS电平转换而来,可以参考Xilinx的官方文档D-PHY solutionsXAPP894,提供了完整D-PHY层的解决方案。

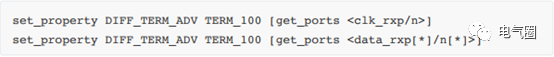

Note1:对于Vivado 2018.2以下的版本,如果MIPI线速率很高,比如1500Mbps,需要在xdc约束文件中添加termination约束,针对Ultrascale芯片,做以下操作:

1. EdgeBoard中使用的是Xilinx Ultrascale+系列的MPSoC,MIPI 的IO必须放置在HP Bank。

2. MIPI_PHY_DCI的电平对Bank的要求苛刻,Bank的VCCO必须设定为1.2V,同时BANK的VREF推荐端接240R。如果Bank中有其他电平标准,比如1.8V的电平,在implementation过程中会报错。

3. MIPI-CSI-RX IP带有Pin assignment的功能,可进行引脚分配的验证,参考后文的MIPI IP 配置。

D-PHY的标准规定总的传输延迟不能超过2 ns,对应到FR4材质的PCB最大的走线长度是25cm到30cm,包括从发送端到接收端,这决定了MIPI支持的传输距离在30cm左右,参考AN-1337D-PHY。同时PCB走线必须匹配100欧姆的端接。

EdgeBoard的MIPI最多支持4通道,可以根据需要选择性使用,用户通过排线与EdgeBoard连接即可,注意排线不要过长,最好小于10cm。

Vivado工具中的视频IP也是在逐步开发完善中,其中难免会遇到各种意想不到的bug,不过好在Xilinx的官方论坛维护地很好,只要发帖提问,短时间内就会得到专门技术人员的回答,同时针对出现的Bug,Xilinx官方也会定期发布相应的patch,Video论坛中积攒的各种帖子也为后续的开发者提供了解决问题的途径。

1. 如果使用2017版本的Vivado,MIPI CSI RX IP不能处理MIPI镜头时钟缺失的问题,参考AR70581。解决该问题,参考AR70530打patch,patch打成功之后,在Vivado软件界面提示AR70530。如果使用2018之后的版本,则不存在这个问题,不需要打patch。

2. MIPI-CSI-RX license 需要购买才能使用,功能验证阶段可以在Xilinx官网申请Evaluation license,但是用evaluation license生成的bit文件,会间歇性停止工作,无法用到真正的产品里面。

License申请参考下文申请Xilinx Evaluation License

3. Github也有开源的MIPI CSI2 IP,该IP针对Xilinx 7 Series FPGA,可以支持到4K的分辨率,采用VHDL开发,但仅支持4通道的MIPI摄像头。

4. 推荐使用2018.3及以上的版本进行MIPI的开发。

1. 根据MIPI摄像头的参数进行基本的设置,主要包括颜色格式、通道数、线速率等。其中线速率最好高于MIPI摄像头的速率,在MIPI IP的内部有一个FIFO缓冲数据,MIPI IP读出速率高于MIPI镜头的写入速度,可以确保不丢帧。

2. 在硬件设计之前就需要进行引脚验证,由于MIPI对于引脚要求相对苛刻,谨慎为好。

前面的MIPI IP只是负责从前端摄像头拿到数据,还需要其他IP进行后续的处理才能得到完整的视频。

也称之为interolation,通过相邻像素的色彩经过插值算法构建出一副标准色彩的图像,实现Bayer到RGB的转换。

摄像头的感光sensor输出的每个像素不是标准的RGB,每个像素只是三原色中的一种,后期通过插值算法恢复出RGB标准颜色,该方法由柯达科学家Bayer博士提出,该方法被称之为Bayer滤色。

感光sensor内部带有color filter array(滤色镜),通过放置不同的原色的filter过滤出单个像素的颜色,每个像素是单个的色彩(RGB中的一种),也称之为RAW数据,后端ISP中通过插值算法恢复到标准的RGB。下图是两种滤色方法,一种是RGB,一种是CMY(印刷四分色模式)。

NOTE:使用Demosaic IP时,需要制定sensor的左上角的第一个像素是什么颜色,不同的sensor起始像素颜色不同。在Demosaic的 BAYER_PHASE (0x0028) Register 中进行设定,参考文档SensorDemosaic。

IP 配置如下:设定每个时钟的像素个数,像素数据宽度以及分辨率。

Gamma矫正的目的是将线性亮度信号或者RGB编码矫正成适合显示器显示的非线性数据。IP使用Gamma LUT,该IP免费,具体配置见下图。

Video process subsystem IP具有视频处理的多种功能,针对MIPI可以使用color space conversion,实现YUV444或者RGB色彩的矫正,提升视觉效果。

注:以上的IP设置均基于Vivado 2017.4版本,2018及以上版本会略有不同,根据我们的开发经验,推荐使用2018.3版本。

EdgeBoard中MIPI摄像头数据流如下图,当用户购买EdgeBoard后,然后搭配我们推荐的MIPI摄像头,即可做到即插即用。

Xilinx MIPI IP和D-PHY对于开发者来说是黑盒子,如果开发中遇到问题,只能通过寄存器的方式来跟踪问题,现介绍一些关键的寄存器。通过跟踪这些寄存器的状态,可以定位排查问题。

首先是判断D-PHY的工作状态,在MIPI IP设置中需要Enable D-PHY Register Interface。

2. CL_STATUS Register(CL -> Clock Lane)

1. 查看clock lane是否处于stop状态

3. DL_STATUS Register (DL -> Data Lane)

1. Core Configuration Register

2. Protocal Configuration Register

1. Lane number:硬件没问题的话,可以看到MIPI摄像头使用的通道数

4. 查看FIFO是否满,如果数据及时读出,是不会出现满的情况

5. Interrupt Status Register

1. 这是排查问题的重要寄存器,各种问题引起的中断都会写入到该寄存器中

6. 如果出现ECC的错误,大概率是硬件信号完整性问题

7. Generic short Packet Register

1. 查看图像格式,在该寄存器能看到对的Data Type,基本可以说明硬件设计没问题

8. Clock Lane Information Register

9. Lane Information Register

1. 查看每个lane的工作状态,每个lane不是始终处于工作状态,也会处于inactive状态

附:申请Xilinx Evaluation License

1. 首先需要有一个Xilinx官方账号,然后进入到Evaluation License网址进行申请,申请界面如下:

2. 点击search now,输入mipi关键字,勾选MIPI RX

3. EvaluationLicense需要绑定主机的MAC地址,点击 GenerateNode-Locked License,然后设置需要绑定的MAC地址

4. 很快在个人注册的邮箱里会收到Xilinx官方发布的lic文件,将其导入到Vivado工具即可。

NOTE:EvaluationLicense仅限于测试MIPI IP和MIPI摄像头的工作状态,不可用于发布产品,其内部带有计数器,连续使用几小时后会停止工作。