在高速电路设计里,我们经常听到一个词——阻抗匹配。尤其是在高多层PCB设计中,阻抗控制几乎是绕不开的话题。那么,为什么PCB高多层板需要做阻抗匹配呢?今天我们就来聊聊这个工程师们都关心的“隐形杀手”。

为什么要做阻抗匹配?

在低速信号电路里,导线更像是一根“导电的铜线”,电流从这头流到那头,不需要太多考虑。

但当信号速度越来越快(频率高、边沿陡),PCB走线就不再是“铜线”,而是变成了传输线。

在传输线上,信号以电磁波的形式传播,此时走线就有了一个固定的特性阻抗。如果信号源、走线、负载之间阻抗不一致,就会产生信号反射,导致波形畸变、时序错误,甚至系统完全无法正常工作。

比如,一条高频走线采用 1oz 厚的铜线布线,线宽为 0.5mm,则会在走线上改变电感、电容和电阻。这给高频信号线带来了困难,因为电容和电感会改变信号的频率,并且走线的终点和起点会产生完全不同的结果,信号会大大衰减。

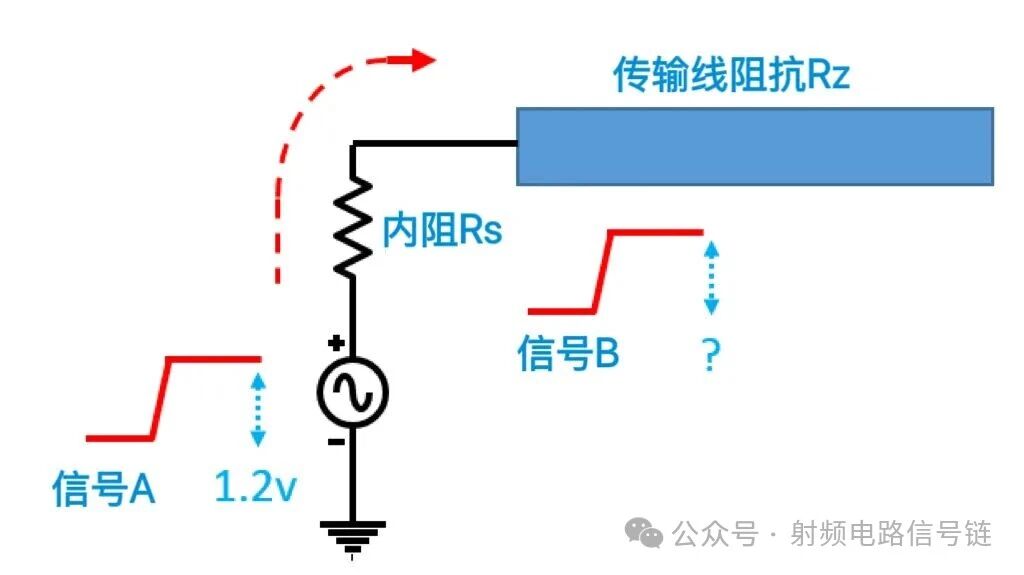

我们再看下面这个图:

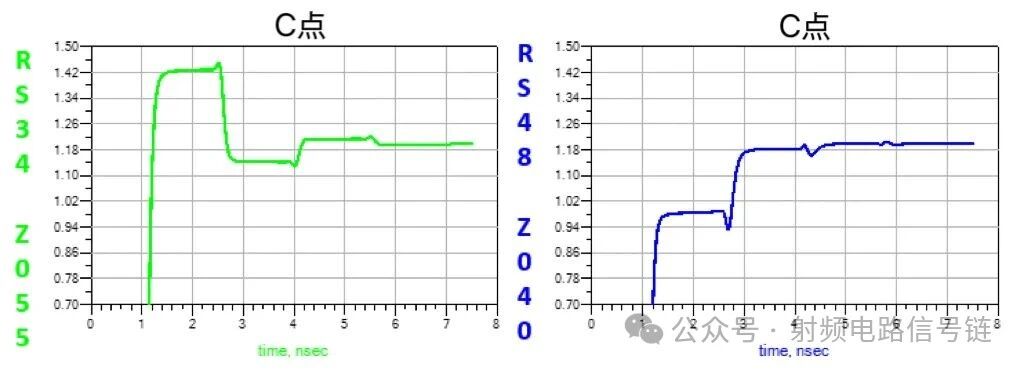

假设信号内阻Rs为48欧姆,传输线内阻为40欧姆,信号A的振幅为1.2V,那到传输线后面B点的振幅就是545mV;如果信号A的驱动能力强一点,内阻降低为34欧姆,那B点的振幅就是649mV。

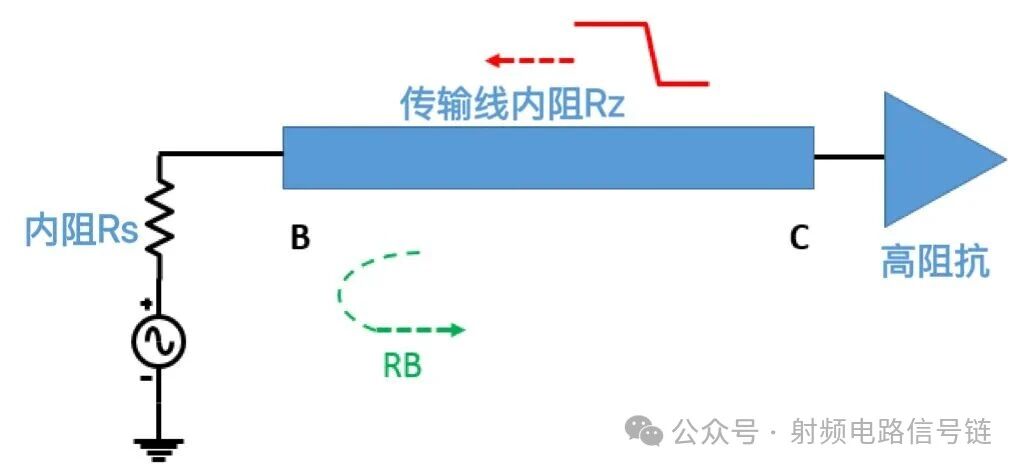

如果传输线后面有一个大阻抗的线路,信号在C点就会被反射。

大家看出来了吧,内阻Rs跟传输线的阻抗,都会对终端的信号产生影响,会导致驱动信号能力不够或者过冲,然后同一组中各种信号到到达终点的时间就会不一样,时序变差,导致信号紊乱或者速度变慢。

简单来说:

-

阻抗匹配好 → 信号传输平稳,眼图漂亮,系统可靠; -

阻抗不匹配 → 反射、串扰、过冲、欠冲一堆问题等着你。

所以,为了确保精心设计信号走线,并且信号质量不会随着走线而下降,不同的地方,我们需要仔细控制不同的阻抗。

阻抗匹配在高多层PCB的意义

高多层板的一个重要作用就是为高速信号提供合理的走线环境。常见的做法是:

-

在信号层下方紧贴一层完整地平面或电源平面; -

通过控制走线宽度、介质厚度、介电常数,形成稳定的特性阻抗; -

让信号沿着确定的路径传播,减少 EMI 和串扰。

所以,在高多层设计中,阻抗匹配不仅是信号完整性(SI)的保障,也是整个板子能否一次性点亮的关键。

工程中常见的阻抗匹配方式

-

端接电阻匹配:最常见的方法,比如在DDR、LVDS、USB差分线上放终端电阻。 -

差分阻抗控制:差分线宽度、间距设计,保证100Ω或90Ω差分阻抗。 -

层叠设计:根据设计要求(如50Ω单端阻抗),在叠层中控制介质厚度和线宽。

常见接口的PCB阻抗要求:

|

|

|

|

|---|---|---|

| 单端信号(如时钟线、控制线) |

|

|

| USB 2.0 (D+/D-) |

|

|

| USB 3.x (SuperSpeed) |

|

|

| HDMI |

|

|

| LVDS |

|

|

| PCIe |

|

|

| SATA |

|

|

| DDR1/2/3/4/5 数据线 |

|

|

| DDR1/2/3/4/5 差分时钟 |

|

|

| Ethernet (100M/1000M/10G) |

|

|

| MIPI DSI/CSI |

|

|

| Thunderbolt/Type-C 高速线 |

|

|

一句话:阻抗匹配不是靠“画好线”就能解决的,而是叠层+走线+仿真综合优化的结果。

案例分享

某开发板采用 DDR3 SDRAM,工作速率 800Mbps。主控芯片与内存芯片之间通过走线连接,包含时钟线、命令/地址线、数据线等。

第一次设计时,工程师只是按常规布线,没有严格控制阻抗:

-

数据线(DQ)实际阻抗在 40Ω~60Ω之间波动;

-

差分时钟线阻抗接近 120Ω(设计偏宽)。

结果:

上电后系统偶尔能跑,但大多数时候死机,示波器抓波形,时钟信号有明显反射和过冲,数据眼图也严重闭合。

工程师对 PCB 进行了 阻抗匹配优化:

-

层叠调整:将信号层下方的参考平面介质厚度缩小,保持数据线阻抗在 50Ω ±10%。

-

差分对优化:重新计算线宽与线间距,将 DDR CK/CK# 差分阻抗控制在 100Ω ±10%。

-

终端电阻:在主控输出端加上 33Ω 串联电阻,抑制过冲。

修改 PCB 并重新打样后,DDR3 系统一次点亮成功,波形测试正常,眼图清晰,系统稳定运行在 800Mbps,反射问题完全消失。